Logic Diagram Of Up Down Counter 31+ Images Result

Logic Diagram Of Up Down Counter. The 2digit up/down counter consists of two seven segment displays connected to atmega8 microcontroller. This can be selected from its input.

Down counting mode m=1 − if m = 1, then the q bar output of the preceding ff is connected to the next ff. Depending on the type of clock inputs, counters are of two types: Or gates are used to combine the outputs of and gate, from each jk flip flop.

1990 f150 wiper switch wiring diagram hydraulic manifold schematic 1997 bmw 840ci fuse box rover 75 ab wiring diagram

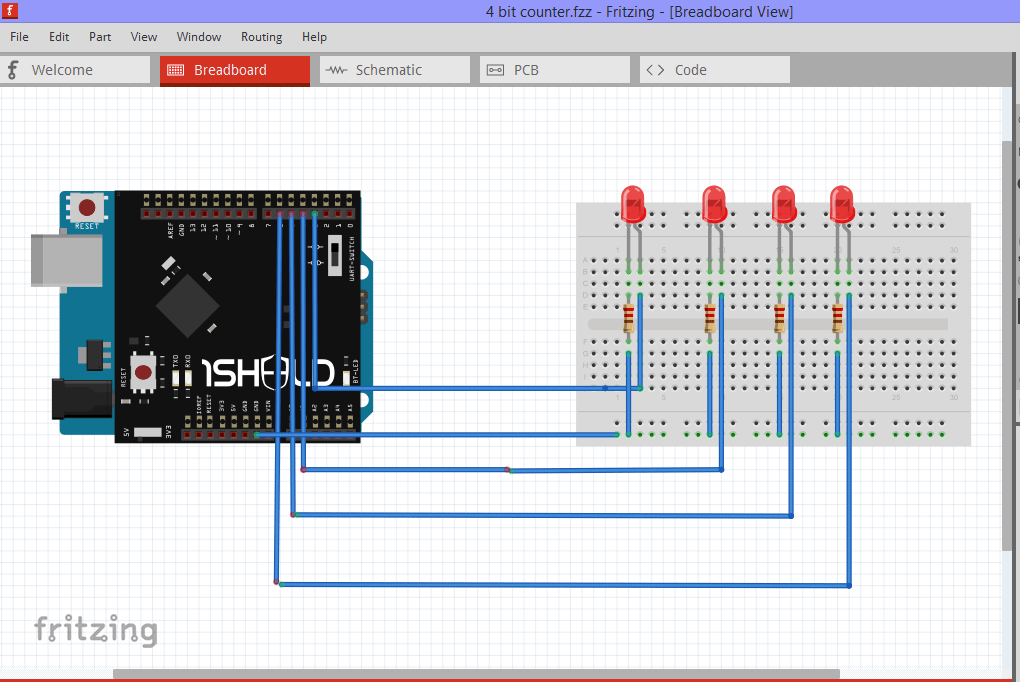

Solved Design A 4bit Updown Counter (as Show In The Tex

Up down counter instruction is used to counting up/down function.cu input is used to get counter enable bool input. It can count in both directions, increasing as well as decreasing. The j and k inputs of 2 flip flops are connected to logic 1. Hence, in this condition the counter will count in down mode, as the input pulses are applied.

Source: zen22142.zen.co.uk

Hence, in this condition the counter will count in down mode, as the input pulses are applied. If the cpd clock is pulsed while cpu is held high, the device. Down by setting the up / down input to logic 1 or 0 respectively. 5.6.10 illustrates how a single input, called (up/ down) can be used to make a single.

![[DIAGRAM] Logic Diagram Of 3 Bit Synchronous Counter FULL [DIAGRAM] Logic Diagram Of 3 Bit Synchronous Counter FULL](https://i2.wp.com/image3.slideserve.com/6160351/a-3-bit-synchronous-binary-counter-n.jpg)

Source: ediagramming.visualacademy.it

If the cpd clock is pulsed while cpu is held high, the device. Or gates are used to combine the outputs of and gate, from each jk flip flop. In this article, we will discuss the circuit, operation and timing diagram of synchronous up counter, synchronous down counter and synchronous up/down counter. Separate count up and count down clocks are.

Source: instrumentationtools.com

The up/ down counter has “up” and “down” count modes by having 2 input and gates, which are used to detect the appropriate bit conditions for counting operation. Cd input is used to get counter enable bool input. This can be selected from its input. Its operating frequency is much higher than the. Hence, in this condition the counter will.

Source: pinterest.com

If the cpu clock is pulsed while cpd is held high, the device will count up. If the up/down input is asserted the counter counts down. S input is used to get the set input, once s input changes from 0 to 1, counter accumulator value changes to 999, which is counter’s higher limit. In the above image, the basic.

Source: youtube.com

Separate up/down clocks, cpu and cpd respectively, simplify operation. If the cpd clock is pulsed while cpu is held high, the device. There are mainly two types of seven segment displays 1) common cathode 2) common anode. When the up / down. Cd input is used to get counter enable bool input.

Source: chegg.com

Or gates are used to combine the outputs of and gate, from each jk flip flop. S input is used to get the set input, once s input changes from 0 to 1, counter accumulator value changes to 999, which is counter’s higher limit. Separate count up and count down clocks are used and in either counting mode the circuits.

Source: multisim.com

We will take a look at all the types of counters and their circuits in detail below. The logic diagram of the synchronous up counter or the given count sequence is drawn as follows. Asynchronous counters and synchronous counters. Up down counter instruction is used to counting up/down function.cu input is used to get counter enable bool input. When the.

Source: circuitdesolator.blogspot.kr

Separate count up and count down clocks are used and in either counting mode the circuits operate synchronously. The seven segment display consists of 8 pins and one common pin. The up/ down counter has “up” and “down” count modes by having 2 input and gates, which are used to detect the appropriate bit conditions for counting operation. If the.

Source: stackoverflow.com

The logic diagram of the synchronous up counter or the given count sequence is drawn as follows. This can be selected from its input. In the above image, the basic synchronous counter design is shown which is synchronous up counter. If the cpu clock is pulsed while cpd is held high, the device will count up. There are mainly two.

Source: electronics.stackexchange.com

The up/ down counter has “up” and “down” count modes by having 2 input and gates, which are used to detect the appropriate bit conditions for counting operation. If the up/down input is asserted the counter counts down. The design of up/ down counter with jk flip flops is shown below. In the above image, the basic synchronous counter design.

Source: plcacademy.com

Asynchronous counters and synchronous counters. Up down counter instruction is used to counting up/down function.cu input is used to get counter enable bool input. If the up/down input is asserted the counter counts down. The design of up/ down counter with jk flip flops is shown below. This can be selected from its input.

Source: radiosparks.com

The logic diagram of the synchronous up counter or the given count sequence is drawn as follows. Cd input is used to get counter enable bool input. This can be selected from its input. 5.6.10 illustrates how a single input, called (up/ down) can be used to make a single counter count either up or down, depending on the logic.

Source: hackster.io

The seven segment display consists of 8 pins and one common pin. The 2digit up/down counter consists of two seven segment displays connected to atmega8 microcontroller. Up down ic counter : This will operate the counter in the counting mode. If the cpu clock is pulsed while cpd is held high, the device will count up.

Source: cssimplified.com

Its operating frequency is much higher than the. There are mainly two types of seven segment displays 1) common cathode 2) common anode. If the cpd clock is pulsed while cpu is held high, the device. Depending on the type of clock inputs, counters are of two types: Down counting mode m=1 − if m = 1, then the q.

Source: zeepedia.com

When the up / down. Normally the counter increments the 4 bit word (q4,q3,q2,q1) by one every time the clock input is toggled. Cd input is used to get counter enable bool input. S input is used to get the set input, once s input changes from 0 to 1, counter accumulator value changes to 999, which is counter’s higher.

Source: wiring121.blogspot.com

The 2digit up/down counter consists of two seven segment displays connected to atmega8 microcontroller. Its operating frequency is much higher than the. The seven segment display consists of 8 pins and one common pin. Depending on the type of clock inputs, counters are of two types: In the above image, the basic synchronous counter design is shown which is synchronous.

Source: wunabarakati-bukutamu.blogspot.com

Internally the counter comprises a set of logic gates configured to implement the arithmetic addition operator (grab the data sheet for the full details). 5.6.10 illustrates how a single input, called (up/ down) can be used to make a single counter count either up or down, depending on the logic state at the up/ down input. The seven segment display.

Source: eduladder.com

Or gates are used to combine the outputs of and gate, from each jk flip flop. When the up / down. Separate up/down clocks, cpu and cpd respectively, simplify operation. Down counting mode m=1 − if m = 1, then the q bar output of the preceding ff is connected to the next ff. There are mainly two types of.

Source: peretas-ilmu.blogspot.com

Or gates are used to combine the outputs of and gate, from each jk flip flop. Its operating frequency is much higher than the. This can be selected from its input. It can count in both directions, increasing as well as decreasing. Depending on the type of clock inputs, counters are of two types:

Source: wiring121.blogspot.com

5.6.10 illustrates how a single input, called (up/ down) can be used to make a single counter count either up or down, depending on the logic state at the up/ down input. Separate count up and count down clocks are used and in either counting mode the circuits operate synchronously. Asynchronous counters and synchronous counters. This will operate the counter.